# 9.5 Control Word Formats

A high on the RESET pin causes all 24 lines of the three 8-bit ports to be in the input mode. All flip-flops are cleared and the interrupts are reset. This condition is maintained even after the RESET goes low. The ports of the 8255 can then be programmed for any other mode by writing a single control word into the control register, when required.

# 9.5.1 For Bit Set/Reset Mode

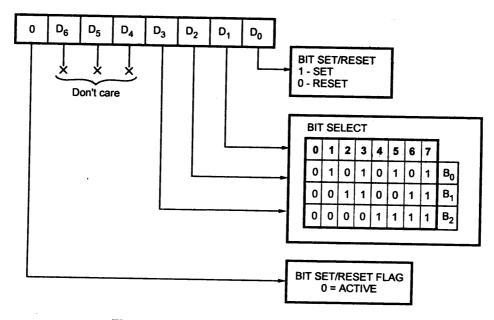

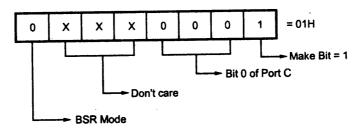

Fig. 9.4 shows bit set/reset control word format.

Fig. 9.4 Bit set/reset control word format

The eight possible combinations of the states of bits  $D_3$ - $D_1$  ( $B_2$   $B_1$   $B_0$ ) in the Bit Set-Reset format (BSR) determine particular bit in  $PC_0$ - $PC_7$  being set or reset as per the status of bit  $D_0$ . A BSR word is to be written for each bit that is to be set or reset. For example, if bit  $PC_3$  is to be set and bit  $PC_4$  is to be reset, the appropriate BSR words that will have to be loaded into the control register will be, 0XXX0111 and 0XXX1000, respectively, where X is don't care.

The BSR word can also be used for enabling or disabling interrupt signals generated by Port C when the 8255 is programmed for Mode 1 or 2 operation. This is done by setting or resetting the associated bits of the interrupts. This is described in detail in next section.

# 9.5.2 For I/O Mode

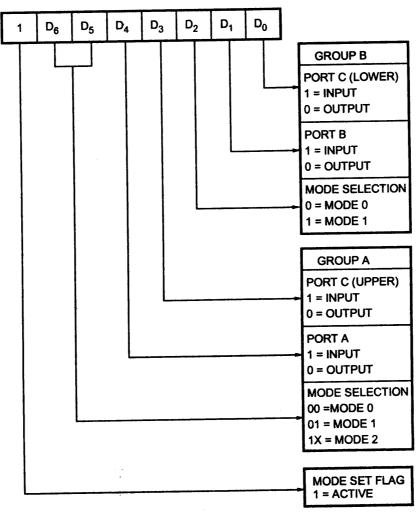

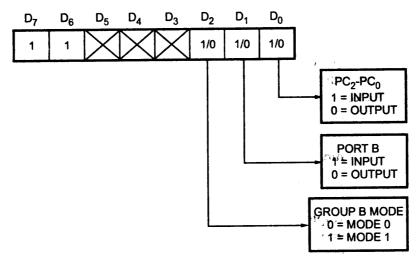

The mode definition format for I/O mode is shown in Fig. 9.5. The control words for both, mode definition and Bit Set-Reset are loaded into the same control register, with bit  $D_7$  used for specifying whether the word loaded into the control register is a mode definition word or Bit Set-Reset word. If  $D_7$  is high, the word is taken as a mode definition word, and if it is low, it is taken as a Bit Set-Reset word. The appropriate bits are set or reset depending on the type of operation desired, and loaded into the control register.

9 - 8

Fig. 9.5 8255 Mode definition format

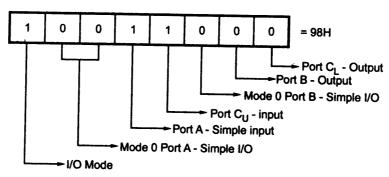

Example 9.1: Write a program to initialize 8255 in the configuration given below:

1. Port A: Simple input

2. Port B: Simple output

3. Port C<sub>1</sub>: Output

4. Port C<sub>U</sub>: Input

Assume address of the control word register of 8255 is 83H.

#### Solution:

Source program:

MOV AL, 98H

; Load control word

OUT 83H, AL

; Send control word

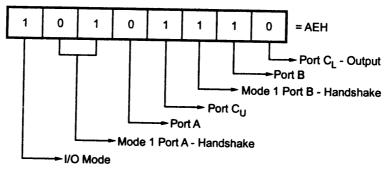

# Example 9.2: Write a program to initialize 8255 in the configuration given below:

1. Port A: Output with handshake

2. Port B: Input with handshake

3. Port C<sub>L</sub>: Output

4. Port C<sub>U</sub>: Input

Assume address of the control word register of 8255 is 23H.

#### Solution:

Source program:

MOV AL, OAEH ; Load control word

OUT 23H,AL ; Send control word

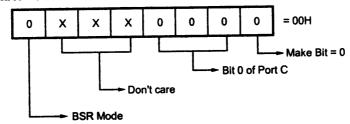

Program: Blink port C bit 0 of 8255.

# **Program Statement:**

Write a program to blink Port C bit 0 of the 8255. Assume address of control word register of 8255 is 83H. Use Bit Set/Reset mode.

# Solution: Control word to make Bit 0 high.

# Control word to make Bit 0 low

## Flow chart:

## Source program:

BACK: MOV AL,01H ; Load bit pattern to make PC<sub>0</sub> high OUT 83H,AL ; Send it to control word register CALL DELAY ; Call Delay subroutine MOV AL,00H ; Load bit pattern to make PC<sub>0</sub> Low OUT 83H,AL ; Send it to control word register CALL Delay ; Call Delay subroutine JMP BACK ; Repeat

# 9.6 8255 Programming and Operation

# 9.6.1 Programming in Mode 0

The Ports A, B and C can be configured as simple input or output ports by writing the appropriate control word in the control word register. In the control word,  $D_7$  is set to '1' (to define a mode set operation) and  $D_6$ ,  $D_5$  and  $D_2$  are all set to '0' to configure all the ports in Mode 0 operation. The status of bits  $D_4$ ,  $D_3$ ,  $D_1$  and  $D_0$  then determine (refer to Fig. 9.5) whether the corresponding ports are to be configured as Input or Output.

For example in mode 0, if Port A and Port B are to operate as output ports with Port C lower as input, and Port C upper as output, the control word that will have to be loaded into the control register will be as follows.

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |       |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|

| 1              | 0              | 0              | 0              | 0              | 0              | 0 .            | 1              | = 81H |

As mentioned earlier, this mode provides simple input and output operations for each of the three ports. No handshaking is required, data is simply written to or read from a specified port.

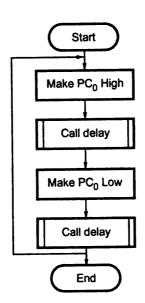

**INPUT MODE:** Fig. 9.6 shows the timing diagram for mode 0 input mode.

Fig. 9.6 Timing diagram for mode 0 input mode

After initialization of 8255 in the input mode 0, CPU can read data through the input port by initiating read command with proper port address. Read command activates RD signal. Upon activation of RD signal CPU reads the data from the selected input port into the CPU register.

## **OUTPUT MODE:**

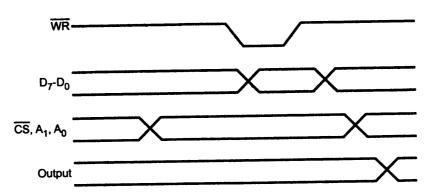

Fig. 9.7 shows the timing diagram for mode 0 output mode.

Fig. 9.7 Timing diagram for mode 0 output mode

After initialization of 8255 in the output mode 0, CPU can write data into the output port by initiating write command with proper port address. CPU sends data on the data bus and upon activation of WR signal, data on the data bus gets latched on the selected output port.

# Mode 0 Configurations:

| -              | Ą              |                | 3              | GRO    | UP A              |    | GRO    | JP B              |

|----------------|----------------|----------------|----------------|--------|-------------------|----|--------|-------------------|

| D <sub>4</sub> | D <sub>3</sub> | D <sub>1</sub> | D <sub>0</sub> | PORT A | PORT C<br>(Upper) | #  | PORT B | PORT C<br>(Lower) |

| 0              | 0              | 0              | 0              | OUTPUT | OUTPUT            | 0  | OUTPUT | OUTPUT            |

| 0              | 0              | 0              | 1              | OUTPUT | OUTPUT            | 1  | OUTPUT | INPUT             |

| 0              | 0              | 1              | 0              | OUTPUT | OUTPUT            | 2  | INPUT  | OUTPUT            |

| 0              | 0              | 1              | 1              | OUTPUT | OUTPUT            | 3  | INPUT  | INPUT             |

| 0              | 1              | 0              | 0              | OUTPUT | INPUT             | 4  | OUTPUT | OUTPUT            |

| 0              | 1              | 0              | 1              | OUTPUT | INPUT             | 5  | OUTPUT | INPUT             |

| 0              | 1              | 1              | 0              | OUTPUT | INPUT             | 6  | INPUT  | OUTPUT            |

| 0              | 1              | 1              | 1              | OUTPUT | INPUT             | 7  | INPUT  | INPUT             |

| 1              | 0              | 0              | 0              | INPUT  | OUTPUT            | 8  | OUTPUT | OUTPUT            |

| 1              | 0              | 0              | 1              | INPUT  | OUTPUT            | 9  | OUTPUT | INPUT             |

| 1              | 0              | 1              | 0              | INPUT  | OUTPUT            | 10 | INPUT  | OUTPUT            |

| 1              | 0              | 1              | 1              | INPUT  | OUTPUT            | 11 | INPUT  | INPUT             |

| 1              | 1              | 0              | 0              | INPUT  | INPUT             | 12 | OUTPUT | OUTPUT            |

| <u>`</u>       | 1              | 0              | 1              | INPUT  | INPUT             | 13 | OUTPUT | INPUT             |

| <del>_</del>   | 1              | 1              | 0              | INPUT  | INPUT             | 14 | INPUT  | OUTPUT            |

| _ <u></u>      | 1              | 1              | 1              | INPUT  | INPUT             | 15 | INPUT  | INPUT             |

## 9.6.2 Programming in Mode 1 (Input / Output with Handshake)

Both Group A and Group B can operate in Mode 1, either together, or individually, with each port containing an 8-bit latched Input or Output data port, and a 4-bit port which is used for control and status of the 8-bit port.

When Port A is to be programmed as an input port,  $PC_3$ ,  $PC_4$  and  $PC_5$  are used for control.  $PC_6$  and  $PC_7$  are not used and can be Input or Output, as programmed by bit  $D_3$  of the control word. When Port A is programmed as an output port,  $PC_3$ ,  $PC_6$ , and  $PC_7$  are used for control and  $PC_4$  and  $PC_5$  can be Input or Output, as programmed by bit  $D_3$ , of the control word.

When port B is to be programmed as an input or output port,  $PC_0$ ,  $PC_1$  and  $PC_2$  are used for control.

#### Mode 1 Input Control Signals:

#### 1. STB (Strobe Input):

This is an active low input signal for 8255 and output signal for the input device. The input device activates this signal to indicate CPU that the data to be read is already sent on the port lines of 8255 port. Upon activation of this signal 8255 loads the data from the input port lines into the input buffer of that port.

#### 2. IBF (Input Buffer Full):

This is an active high output signal for 8255 and an input signal for input device. This signal is generated by 8255 in response to  $\overline{STB}$  signal as an acknowledgment to input device. It also indicates to the input device that the input buffer is full and it is not ready to accept next byte from the input device. Therefore input device sends data on the port lines only when IBF signal is not active. The IBF signal is deactivated when CPU reads the data from input buffer of the respective port by activation of  $\overline{RD}$  signal.

#### 3. INTR (Interrupt Request):

This is an active high output signal generated by 8255. A 'high' on this output can be used to interrupt the CPU when an input device is requesting service. The 8255 sets the INTR when STB signal is 'one', IBF signal is 'one' and INTE is 'one', indicating CPU that the data from the input device is available in the input buffer. This signal is reset by the falling edge of the RD signal i.e. immediately after reading the data from the input buffer.

INTE (Interrupt Enable) flip-flop is used to enable or disable INTR (Interrupt request) signal. If INTE flip-flop is set, the interrupt request is generated depending on the status of STB and IBF signals. If INTE flip-flop is reset, the interrupt request is not generated, allowing masking facility for the interrupt.

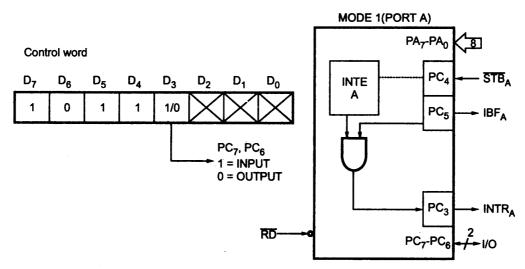

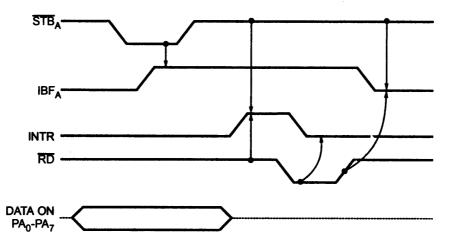

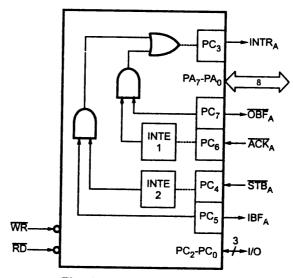

#### Mode 1 : Port A Input Operation

Fig. 9.8 (a) shows Port A as an input port along with the control word and control signals (for handshaking with a peripheral). When the control word (as in Fig. 9.8 (a) is loaded into the control register, Group A is configured in Mode 1 with Port A as an input port. Port A can accept parallel data from a peripheral (like a keyboard) and this data can be read by the CPU. The peripheral first loads data into Port by making the  $\overline{STB}_A$  input low. This latches the data placed by the peripheral on the common data bus into Port A. Port A acknowledges reception of data by making IBF<sub>A</sub> (Input Buffer Full) high. IBFA is set when the  $\overline{STB}_A$  input is made low, as shown in Fig. 9.8 (b).

Fig. 9.8 (a) Port A in mode 1

Fig. 9.8 (b) Timing diagram for port A in mode 1

INTR<sub>A</sub> is an active high output signal which can be used to interrupt the CPU so that the CPU can suspend its current operation and read the data written into Port A by the

peripheral. INTRA can be enabled or disabled by the INTEA flip-flop which is controlled by Bit Set-Reset operation of PC4. INTRA is set (if enabled by setting the INTEA flip-flop) after the STBA has gone high again, and if IBFA is high.

On receipt of the interrupt, the CPU can be forced to read Port A. The falling edge of the RD input resets IBFA and it goes low. This can be used to indicate to the peripheral that the input buffer is empty and that data can again be loaded into it.

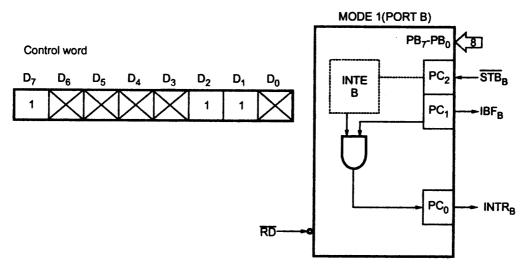

# Mode 1 : Port B Input operation

Fig. 9.9 shows Port B as an input port (when in Mode 1). The timing diagram and operation of Port B is similar to that of Port A except that it uses different bits of Port C for control. INTE<sub>B</sub> is controlled by Bit Set/Reset of PC<sub>2</sub>.

Fig. 9.9 Port B in mode 1

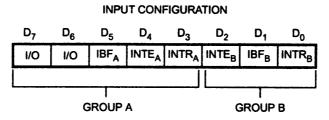

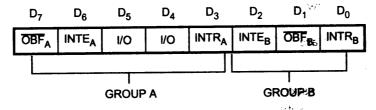

If the CPU is busy with other system operations, it can read data from the input port when it is interrupted. This is often called Interrupt driven I/O. However, if the CPU is otherwise not busy with other jobs, it can continuously poll (read) the status word to check for an IBFA. This is often called Program Controlled I/O. The status word is accessed by reading Port C (A1 A0 must be 10, RD and CS must be low). The status word format when Ports A and B are input ports in Mode 1, is shown in Fig. 9.10.

Fig. 9.10 Mode 1 status word (Input)

# Mode 1 : Output control signals

#### 1. OBF (Output Buffer Full) :

This is an active low output signal for 8255 and input signal for the output device. The 8255 activates this signal to indicate output device that data is available on the output port. Upon activation of  $\overline{OBF}$  signal, output device reads data from the output port and acknowledges it by  $\overline{ACK}$  signal. The  $\overline{OBF}$  signal is activated at the rising edge of the  $\overline{WR}$  signal and de-activated at the falling edge of the  $\overline{ACK}$  signal.

# 2. ACK (Acknowledge Input):

This is an active low input signal for 8255 and output signal for the output device. The output device generates this signal to indicate 8255 that the data from port A or Port B has been accepted.

#### 3. INTR (Interrupt Request):

This is an active high output signal generated by 8255. A 'high' on this output can be used to interrupt the CPU when an output device has accepted data transmitted by the CPU. The 8255 sets the INTR when  $\overline{ACK}$  signal is 'one',  $\overline{OBF}$  is 'one' and INTE is 'one', indicating that the output device is ready to accept next data byte. 'This signal is reset by the falling edge of the  $\overline{WR}$  signal i.e. immediately after sending the data to the output port.

INTE (Interrupt Euclie) flip-flop is used to enable or disable INTR (Interrupt Request) signal. If INTE flip-flop is set, the interrupt request is generated depending on the status of ACK and OBF signals. If INTE flip-flop is reset, the interrupt request is not generated, allowing masking facility for the interrupt.

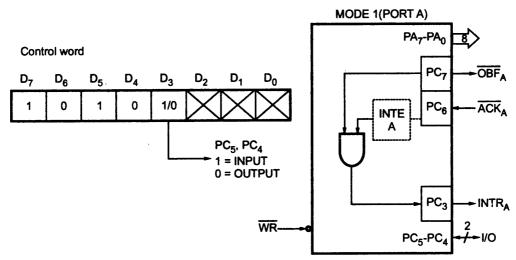

#### Mode 1: Port A output operation

Fig. 9.11 (a) Port A in mode 1

the control word and control signals (for handshaking with a peripheral). When the control word (as in Fig. 9.11 (a)) is loaded into the control register, Group A is configured in Mode 1 with Port A as an output port. The CPU can send data to a peripheral (like a display device) through Port A of the 8255.

9 - 17

Fig. 9.11 (b) Port A in mode 1 (Output)

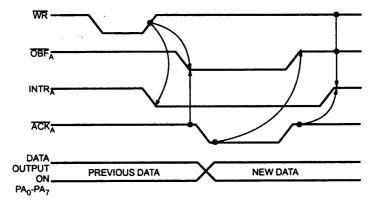

The  $\overline{OBF}_A$  output (Output Buffer Full) goes low on the rising edge of the  $\overline{WR}$  signal (when the CPU writes data into the 8255). The  $\overline{OBF}_A$  output from 8255 can be used as a strobe input to the peripheral to latch the contents of Port A. The peripheral responds to the receipt of data by making the  $\overline{ACK}_A$  input of the 8255 low, thus acknowledging that it has received the data sent by the CPU through Port A. The  $\overline{ACK}_A$  low sets the OBFA signal, which can be polled by the CPU through OBFA of the status word to load the next data when it is high again.

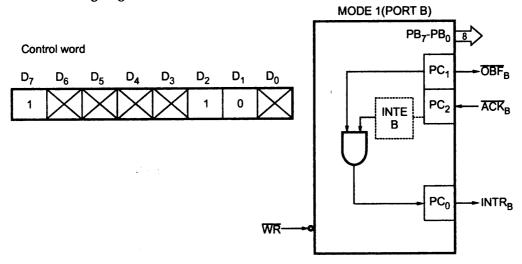

Fig. 9.12 Port B in mode 1 (Output)

INTR<sub>A</sub> is an active high output of the 8255 which is made high (if the associated INTE<sub>A</sub> flip-flop is set) when  $\overline{ACK}_A$  is made high again by the peripheral, and when  $\overline{OBF}_A$

goes high again (see timing diagram in Fig. 9.11). It can be used to interrupt the CPU whenever the output buffer is empty. It is reset by the falling edge of  $\overline{WR}$  when the CPU writes data onto Port A. It can be enabled or disabled by writing  $a^{1/2}$  or a '0' respectively to PC<sub>6</sub> in the BSR mode.

9 - 18

# Mode 1: Port B output operation

Fig. 9.12 shows Port B as an output port when in Mode 1. The operation of Port B is similar to that of Port A. INTR<sub>A</sub> is controlled by writing a '1' or a '0' to PC<sub>2</sub> in the BSR mode.

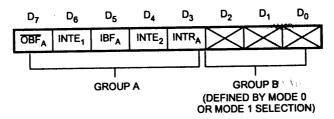

The status word is accessed by issuing a Read to Port C. The format of the status word when Ports A and B are Output ports in Mode 1 is shown in Fig. 9.13.

Fig. 9.13 Mode 1 status word (Output)

# 9.7 Programming in Mode 2 (Strobes Bi-directional Bus I/O)

When the 8255 is operated in Mode 2 (by loading the appropriate control word), Port A can be used as a bi-directional 8-bit I/O bus using for handshaking. Port B can be programmed in Mode 0 or in Mode 1. When Port B is programmed in mode 1,  $PC_0 - PC_2$  lines of Port C are used as handshaking signals.

Fig. 9.14 Mode 2 control word

Fig. 9.14 shows the control word that should be loaded into the control port to configure 8255 in Mode 2.

# Mode 2 : Control signals

INTR (Interrupt Request): A 'high' on this output can be used to interrupt the CPU for input or output operations.

# **Output Control Signals:**

# OBF<sub>A</sub> (Output Buffer Full)

This is an active low output which indicates that the CPU has written data into Port A.

# ACK<sub>A</sub> (Acknowledge)

This is an active low input signal (generated by the peripheral) which enables the tri-state output buffer of Port A and makes Port A data available to the peripheral. In Mode 2, Port A outputs are in tri-state until enabled.

#### INTE 1

This is the flip-flop associated with Output Buffer Full. INTE 1 can be used to enable or disable the interrupt by setting or resetting  $PC_6$  in the BSR Mode.

## Input Control Signals:

# STB (Strobe Input)

This is an active low input signal which enables Port A to latch the data available at its input.

# IBF (Input Buffer Full Flip-Flop)

This is an active high output which indicates that data has been loaded into the input latch of Port A.

#### INTE 2

This is an Interrupt enable flip-flop associated with Input Buffer Full. It can be controlled by setting or resetting PC<sub>4</sub> in the BSR Mode.

# Mode 2: Port A operation.

Fig. 9.15 shows Port A and associated control signals when 8255 is in Mode 2. Interrupts are generated for both output and input operations on the same INTR<sub>A</sub> (PC<sub>3</sub>) line.

Fig. 9.15 Mode 2 operation

# Status Word in Mode 2

The status word for Mode 2 (accessed by reading Port C) is shown in Fig. 9.15.  $D_7$ - $D_3$  of the status word carry information about  $\overline{OBF}_A$ ,  $INTE_1$ ,  $IBF_A$ ,  $INTE_2$ ,  $INTR_A$ . The status of the bits  $D_2$  -  $D_0$  depend on the mode setting of Group B. If B is programmed in Mode 0,  $D_2$  -  $D_0$  are the same as  $PC_2$  -  $PC_0$  (simple I/O); however if B is in Mode 1,  $D_2$  -  $D_0$  carry information about the control signals for Port B (as in Fig. 9.10, or Fig. 9.13), depending upon whether Port B is an Input port or Output port respectively.

Fig. 9.16 Status word for mode 2

# **Mode Definition Summary**

|                                                                                                                                                      | MOD                                   | E 0                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------|

|                                                                                                                                                      | IN                                    | OUT                                           |

| PA <sub>0</sub><br>PA <sub>1</sub><br>PA <sub>2</sub><br>PA <sub>3</sub><br>PA <sub>4</sub><br>PA <sub>5</sub><br>PA <sub>6</sub><br>PA <sub>7</sub> | 222222                                | OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT |

|                                                                                                                                                      | MOL                                   | )E 0                                          |

|                                                                                                                                                      | IN                                    | OUT                                           |

| PB <sub>0</sub><br>PB <sub>1</sub><br>PB <sub>2</sub><br>PB <sub>3</sub><br>PB <sub>4</sub><br>PB <sub>5</sub><br>PB <sub>6</sub><br>PB <sub>7</sub> | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z | OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT |

| PC0<br>PC1<br>PC2<br>PC3<br>PC4<br>PC5<br>PC6<br>PC7                                                                                                 | Z                                     | OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT |

| MOD                                                                                                             | E 1                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| IN                                                                                                              | OUT                                                                                                             |

| 222222                                                                                                          | 01<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>00<br>0                                 |

| MO                                                                                                              | )E 1                                                                                                            |

| IN                                                                                                              | OUT                                                                                                             |

|                                                                                                                 | OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT                                                                   |

| INTR <sub>B</sub> IBF <sub>B</sub> STB <sub>B</sub> INTR <sub>A</sub> STB <sub>A</sub> IBF <sub>A</sub> I/O I/O | INTR <sub>B</sub> OBF <sub>B</sub> ACK <sub>B</sub> INTR <sub>A</sub> I/O I/O ACK <sub>A</sub> OBF <sub>A</sub> |

| MODE 2                        |            |

|-------------------------------|------------|

| GROUP A ON                    | ILY        |

| $\leftrightarrow$             |            |

| $\leftrightarrow$             |            |

| $\leftrightarrow$             |            |

| <b>↔</b>                      |            |

| ↔                             |            |

| $\leftrightarrow$             |            |

| . ↔                           |            |

| MODE 2                        |            |

| GROUP A ON                    | <b>ILY</b> |

| -                             |            |

| _                             |            |

| _                             |            |

| -                             |            |

| _                             |            |

| _                             |            |

| _                             |            |

| VO                            |            |

| νo                            |            |

| 1/0                           |            |

| INTRA<br>STBA<br>IBFA<br>ACKA |            |

| SIBA                          |            |

| ACK.                          |            |

| OBF <sub>A</sub>              |            |

|                               |            |

Mode 0 or Mode 1 Only The 8086 has four special instructions IN, INS, OUT, and OUTS to transfer data through the input/output ports in I/O mapped I/O system.  $M/\overline{IO}$  signal is always low when 8086 is executing these instructions. So  $M/\overline{IO}$  signal is used to generate separate addresses for, memory and input/output. Only 256 (2<sup>8</sup>) I/O addresses can be generated when direct addressing method is used. By using indirect address method this range can be extended upto 65536 (2<sup>16</sup>) addresses.

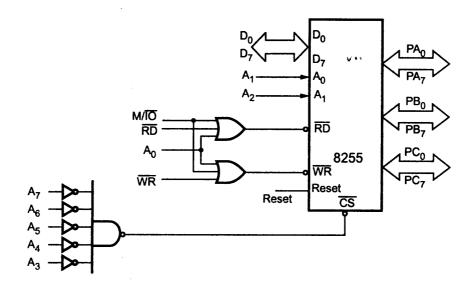

Fig. 9.17 shows the interfacing of 8255 with 8086 in I/O mapped I/O technique. Here,  $\overline{RD}$  and  $\overline{WR}$  signals are activated when M/ $\overline{IO}$  signal is low, indicating I/O bus cycle. Only lower data bus (D<sub>0</sub> - D<sub>7</sub>) is used as 8255 is 8-bit device. Reset out signal from clock generator is connected to the Reset signal of the 8255. In case of interrupt driven I/O INTR signal (PC<sub>3</sub> or PC<sub>0</sub>) from 8255 is connected to INTR input of 8088.

Fig. 9.17 I/O mapped I/O

## I/O Map:

| Port / control Register |                |                | Add            | res            | s lir          | 105            |                |                | Address |

|-------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

|                         | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |         |

| Port A                  | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 00H     |

| Port B                  | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 02H     |

| Port C                  | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 04H     |

| Control register        | 0              | 0              | 0              | 0              | 0              | 1              | 1              | 0              | 06H     |

Note: It is assumed that the direct addressing is used.

# 9.9 Interfacing 8255 to 8086 in Memory Mapped I/O

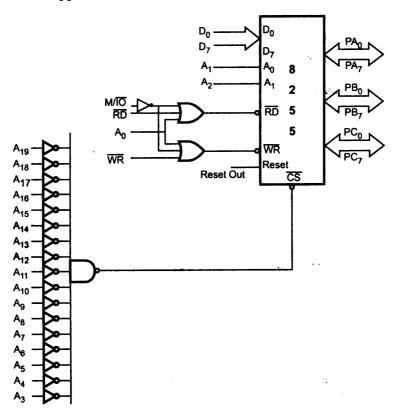

In this type of I/O interfacing, the 8086 uses 20 address lines to identify an I/O device; an I/O device is connected as if it is a memory register. The 8086 uses same control signals and instructions to access I/O as those of memory. Fig. 9.18 shows the interfacing of 8255 with 8086 in memory mapped I/O technique. Here  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals are activated when M/ $\overline{\text{IO}}$  signal is high, indicating memory bus cycle. Address lines A  $_0$  - A  $_1$  are used by 8255 for internal decoding. To get absolute address, all remaining address lines (A $_3$  - A $_{19}$ ) are used to decode the address for 8255. Other signal connections are same as in I/O mapped I/O.

Fig. 9.18 Memory mapped I/O

### I/O Map:

| Register         | A19 | A <sub>18</sub> | A <sub>17</sub> | A <sub>16</sub> | A <sub>16</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A, | As | <b>A</b> <sub>7</sub> | As | As | A, | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Ao | Address |

|------------------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|----|-----------------------|----|----|----|----------------|----------------|----------------|----|---------|

| Port A           | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0  | 0                     | 0  | 0  | 0  | 0              | 0              | 0              | 0  | 00000Н  |

| Port B           | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0  | 0                     | 0  | 0  | 0  | 0              | 0              | 1              | 0  | 00002H  |

| Port C           | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0  | 0                     | 0  | 0  | 0  | 0              | 1              | 0              | 0  | 00004H  |

| Control register | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0  | 0                     | 0  | 0  | 0  | 0              | 1              | 1              | 0  | 00006Н  |

# 9.10 Interfacing 8255 to 8088 in I/O Mapped I/O Mode

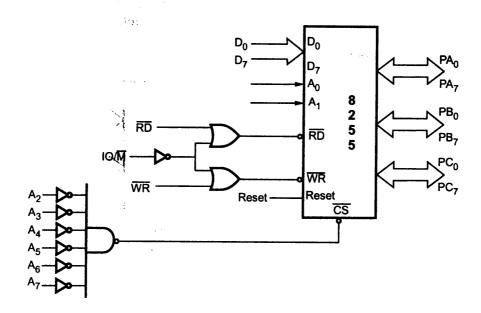

Fig. 9.19 shows the interfacing of 8255 with 8088 in I/O mapped I/O technique. Here,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals are activated when IO/ $\overline{\text{M}}$  signal is high, indicating I/O bus cycle. Address lines  $A_0$  and  $A_1$  are connected to  $A_0$  and  $A_1$  lines of 8255. The reset out signal from clock generator is connected to the reset input of the 8255.

Fig. 9.19 Interfacing 8255 to 8088 in I/O mapped I/O

In case of interrrupt driven I/O, INTR signal ( $PC_3$  or  $PC_0$ ) from 8255 is connected to INTR input of 8089.

# I/O map:

| Port / Control register |                |                | Ad             | dres           | s lir          | 105            |                |                | Address |

|-------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

|                         | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |         |

| Port A                  | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 00Н     |

| Port B                  | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 01H     |

| Port C                  | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 02H     |

| Control Register        | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1              | 03H     |

Note: it assumed that the direct addressing is used.

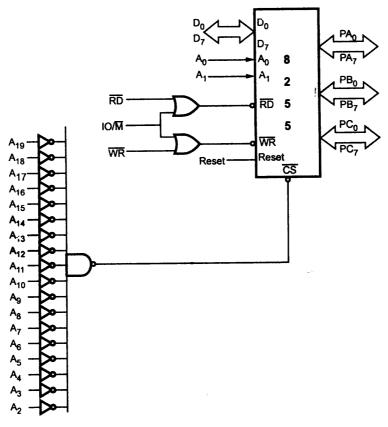

# 9.11 Interfacing 8255 to 8088 in Memory Mapped I/O

In this type of I/O interfacing, the 8088 uses 20 address lines to identify an I/O device; an I/O device is connected as if it is a memory register. The 8088 uses same control signals and instructions to access I/O as those of memory. Fig. 9.20 shows the interfacing of 8255 with 8088 in memory mapped I/O technique. Here  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals are activated when IO/ $\overline{\text{M}}$  signal is low, indicating memory bus cycle. Address lines  $A_0$ - $A_1$  are used by 8255 for internal decoding. To get absolute address, all remaining address lines ( $A_2$ - $A_{19}$ ) are used to decode the address for 8255. Other signal connections are same as in I/O mapped I/O.

Fig. 9.20 Memory mapped I/O

# I/O Map:

| Register         | A <sub>1</sub> 9 | A <sub>18</sub> | A <sub>17</sub> | A <sub>16</sub> | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A, | A | A7 | As | A <sub>5</sub> | A4 | A <sub>3</sub> | $\mathbf{A_2}$ | $\mathbf{A_1}$ | A, | Address |

|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|---|----|----|----------------|----|----------------|----------------|----------------|----|---------|

| Port A           | 0                | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0 | 0  | 0  | 0              | 0  | 0              | 0              | 0              | 0  | 00000   |

| Port B           | 0                | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0 | 0  | 0  | 0              | 0  | 0              | 0              | 0              | 1  | 00001F  |

| Port C           | 0                | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0 | 0  | 0  | 0.             | 0  | 0              | 0              | 1              | 0  | 00002F  |

| Control Register | 0                | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0  | 0 | 0  | 0  | 0              | 0  | 0              | 0              | 1              | 1  | 00003F  |

# 9.12 Centronics Parallel Printer Interface

As explained earlier, handshaking signals are required to transfer data between two devices whose speeds are not same. This centronics protocol is a printer protocol, gives standards for printer interface.

It has 36 pins. The Fig. 9.21 shows the pin definitions for centronics interface. The ASCII characters are sent to the printer through eight data lines. Each data line has individual ground to reduce the change of picking up electrical noise in the lines.

| Signal<br>Pin<br>No. | Reutrn<br>Pin No. | Signal          | Direction | Description                                                                                                                                                                                                                                          |

|----------------------|-------------------|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | 19                | STROBE          | IN        | STROBE pulse to read data in. Pulse width must be more than 0.5 ms at receiving terminal. The signal level is normally "high": read-in of data is performed at the "low" level of this signal.                                                       |

| 2                    | 20                | DATA 1          | IN        |                                                                                                                                                                                                                                                      |

| 3                    | 21                | DATA 2          | IN        |                                                                                                                                                                                                                                                      |

| 4                    | 22                | DATA 3          | IN        |                                                                                                                                                                                                                                                      |

| 5                    | 23                | DATA 4          | IN        |                                                                                                                                                                                                                                                      |

| 6                    | 24                | DATA 5          | IN        |                                                                                                                                                                                                                                                      |

| 7                    | 25                | DATA 6          | IN        | These signals represent information of the 1st to 8th this of                                                                                                                                                                                        |

| 8                    | 26                | DATA 7          | IN        | parallel data respectively. Each signal is at "high" level when data logical "i" and "low" when logical "0".                                                                                                                                         |

| 9                    | 27                | DATA 8          | IN        | data logical i and low when logical o.                                                                                                                                                                                                               |

| 10                   | 28                | ACKNLG          | OUT       | Approximately 5 ms pulse; "low" indicates that data has been received and the printer is ready to accept other data.                                                                                                                                 |

| 11                   | 29                | BUSY            | OUT       | A "high" signal indicates that the printer cannot receive data The signal becomes "high" in the following cases:  1. During data entry.  3. In "office" state.  2. During printing operation.4. During printer error status.                         |

| 12                   | 30                | PE              | OUT       | A "high" signal indicates that the printer is out of paper.                                                                                                                                                                                          |

| 13                   |                   | SLCT            | OUT       | This signal indicates that the printer is in the selected state.                                                                                                                                                                                     |

| 14                   |                   | AUTO<br>FEED XT | IN        | When this signal being at "low" level, the paper is automatically fed one line after printing. (The signal level can be fixed to "low" with DIP SW pin 2-3 provided on the control circuit board).                                                   |

| 15                   |                   | NC              |           | Not used.                                                                                                                                                                                                                                            |

| 16                   |                   | OV              |           | Logic GND level.                                                                                                                                                                                                                                     |

| 17                   |                   | CHASIS-<br>GND  |           | Printer chasis GND. In the printer, the chasis GND and the logic GND are isolated from each other.                                                                                                                                                   |

| 18                   |                   | NC              |           | Not used.                                                                                                                                                                                                                                            |

| 19-30                |                   | GND             |           | "Twisted-Pair Return" signal; GND level.                                                                                                                                                                                                             |

| 31                   |                   | INIT            | IN        | When the level of this signal becomes "low" the printer controller is reset to its initial state and the print buffer is cleared. This signal is normally at "high" level and its pulse with must be more then 50 $\mu s$ at the receiving terminal. |

| 32 | <br>ERROR   | OUT | The level of this signal becomes "low" when the printer is in "Paper End" state. "Offline" state and "Error" state.                                                                                         |

|----|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33 | <br>GND     | -   | Same as with pin numbers 19 to 30.                                                                                                                                                                          |

| 34 | <br>NC      | -   | Not used.                                                                                                                                                                                                   |

| 35 |             |     | Pulled up to + 5V <sub>dc</sub> through 4.7 K-ohms resistance.                                                                                                                                              |

| 36 | <br>SLCT IN | IN  | Data entry to the printer is possible only when the level of this signal is "low". (Internal fixing can be carried out with DIP SW 1-8. The condition at the time of snpment is set "low" for this signal). |

#### Notes:

- 1. "Direction" refers to the direction off signal flow as viewed from the printer.

- 2. "Return" denotes "Twisted-Pair Return" and is to be connected at signal-ground level.

- When wikring the interface, be sure to use a twisted-pair cable for each signal and never fail to complete connection on the return side to prevent noise effectively, these cables should be shielded and connected to the chassis of the system unit.

- 3. All interface conditions are based on TTL level. Both the rise and fall times of each signal must be less than  $0.2 \mu s$ .

- 4. Data transfer must not be carried out by ignoring the ACKNLG or BUSY signal. (Data transfer to this printer can be carried out only after confirming the ACKNLG signal or when the level of the BUSY signal is "low".

#### Fig. 9.21 Pin definitions for centronics interface

The other signals fall into two categories, signals sent to the printer to tell it which operation to do and signals from the printer that indicate its status. These signals are as follows:

#### a) Input signals for printer:

- 1. INIT: This signal when activated tells the printer to perform its internal initialization sequence.

- 2. STROBE (STB): This signal when activated tells the printer that valid data is available on the data bus.

#### b) Status signals output from printer:

- 1. ACK: This signal when low indicates that the data character has been accepted and the printer is ready for the next data.

- 2. BUSY: This is active high signal. It goes high when printer is not ready to receive a character.

- 3. PE: This active high signal goes high when printer is out of paper.

- 4. SLCT: This signal goes high if the printer is selected for receiving data.

- 5. ERROR: This active low signal goes low for variety of problem conditions in the printer.

9 - 27

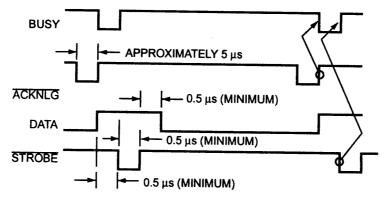

Fig. 9.22 shows the timing waveforms for transfer of data characters to an IBM printer using the basic handshake signals.

Fig. 9.22 Timing waveforms for transfer of data characters to an IBM printer

# **Communication between Computer and Printer**

Computer sends the INIT pulse for atleast 50 µs, to initialize the printer. Computer then checks for BUSY low to confirm whether the printer is ready to receive data or not. If BUSY signal is low (not busy), computer sends an ASCII code on eight parallel data lines and after at least 0.5 μs, it also sends STB signal to indicate, valid data is available on the data bus. Computer activates this STB signal for at least 0.5 µs and it also ensures that valid data is present on the data bus for at least 0.5  $\mu s$  after the  $\overline{STB}$  signal is disabled. When the printer is ready to receive the next character, it asserts its ACK signal low for about 5  $\mu s$ . The rising edge of the  $\overline{ACK}$  signal tells the computer that it can send the next character. The rising edge of the ACK signal also resets the BUSY signal from the printer. When computer finds busy low, it sends the next character along with strobe and the sequence is repeated till the last character transfer.

# Centronics Printer Interface using 8255

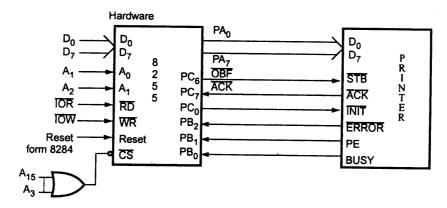

Fig. 9.23 shows the circuit for interfacing centronix type parallel input printer to 8255A. Port A is used to send 8-bit data to the printer. It is used in mode 1 so PC6

Fig. 9.23 Interfacing centronix printer to 8255A

$(\overline{OBF} \text{ signal})$  is used as  $\overline{STB}$  signal to tell the printer that valid data is available on the data bus and PC<sub>7</sub> is used as an  $\overline{ACK}$  signal. BUSY, PE and  $\overline{ERROR}$  signals are connected to the PB<sub>0</sub> to PB<sub>2</sub> port lines.

In the next section we will see flowchart and program required to print a message.

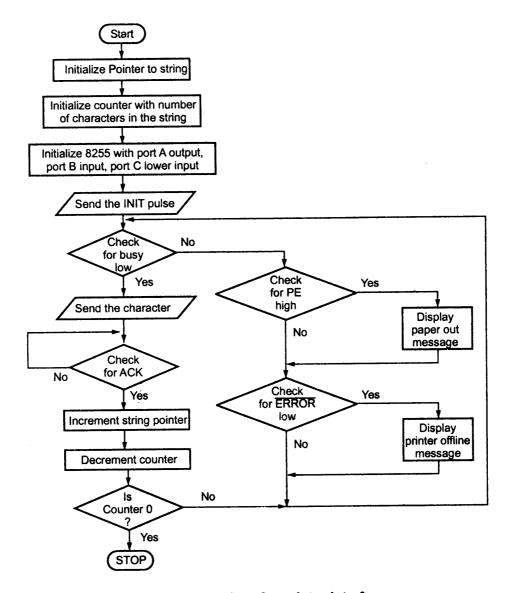

#### Flowchart:

Fig. 9.24 Flowchart for printer interface.

Fig. 9.24 Flowchart for printer interface

In the program it is necessary to initialize 8255 as follows

| Port       | Input/output | Mode |

|------------|--------------|------|

| Port A     | Output       | 1    |

| Port B     | Input        | 0    |

| Port Upper | _            | ***  |

| Port Lower | Output       |      |

#### Control word:

| 1/0 | Mode A |   | PA PCU |   | Mode B | PB | PCL |       |

|-----|--------|---|--------|---|--------|----|-----|-------|

| 1   | 0      | 1 | 0      | Х | 0      | 1  | 0   | = A2I |

#### I/O map :

| A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Address | Port   |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|--------|

| 0               | 0               | 0               | 0               | 0               | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0000H   | Port A |

| 0               | 0               | 0               | 0               | 0               | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0002H   | Port B |

| 0               | 0               | 0               | 0               | 0               | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0004H   | Port C |

| 0               | 0               | 0               | 0               | 0               | 0               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1              | 0              | 0006H   | CR     |

## Program:

```

.MODEL SMALL

PortA

EQU

0000

PortB

EQU

0002

PortC

EQU

0004

CR

EQU

0006

.DATA

Mes1

DB 'Printer Paper Out', 10, 13, '$'

DB 'Printer Offline', 10, 13, '$'

Mes2

DB 'Printing Over', '$'

Mes3

DB 'This is to be print'

Mes4

COUNT

DB 15

.CODE

START:

VOM

AX, @DATA

; Initialize data segment

MOV

DS, AX

LEA

BX,MES4

; Initialize pointer to string

VOM

DX,CR

; CR is control register address

VOM

AL, OA2H

; Load control word

OUT

DX,AL

MOV

AL,07

; Make INTE_A high to enable INTR_A

DX, AL

OUT

MOV

AL,00

; Make PC_0 = \frac{1ow}{INIT} (BSR mode) ; to give INIT low

DX,AL

OUT

MOV

CX, OFFFH

```

| BACK:   | DEC      | СХ        | ; Wait for more than 50 μs                      |

|---------|----------|-----------|-------------------------------------------------|

|         | LOOP BAC | K         |                                                 |

|         | MOV      | AL,01     |                                                 |

|         | OUT      | DX,AL     | ; Make INIT HIGH                                |

| NEXT:   | MOV      | DX, PortB |                                                 |

|         | IN       | AL, DX    |                                                 |

|         | MOV      | AH,AL     | ; Save status information                       |

|         | AND      | AL,01H    |                                                 |

|         | JNZ      | CHECK     | ; Check for BUSY if high goto                   |

|         |          |           | ; check                                         |

|         | MOV      | AL,[BX]   |                                                 |

|         | MOV      | DX, PortA |                                                 |

|         | OUT      | DX,AL     | ; Send the character                            |

|         | MOV      | DX, PortC |                                                 |

| AGAIN:  | IN       | AL, DX    | ; Check for ACK by                              |

|         | AND      | AL,08     | ; checking $\mathtt{INTR}_\mathtt{A}$ line high |

|         | JZ       | AGAIN     |                                                 |

|         | INC      | BX        | ; Increment string pointer                      |

|         | MOV      | AL, COUNT |                                                 |

|         | DEC      | AL        |                                                 |

|         | MOV      | COUNT, AL | ; Decrement counter                             |

|         | JNZ      | NEXT      | ; Check for counter = 0                         |

|         | JMP      | LAST      |                                                 |

| CHECK:  | MOV      | AL,AH     |                                                 |

|         | AND      | AL,02     |                                                 |

|         | VOM      | AL,AH     | ; Save printer status                           |

|         | JZ       | CHECK1    |                                                 |

|         | LEA      | DX,MES1   |                                                 |

|         | MOV      | АН,09Н    | ; Call for DOS interrupt                        |

|         | INT 21H  |           | ; to display MES1                               |

| CHECK1: | AND      | AL,04     |                                                 |

|         | JNZ      | NEXT      |                                                 |

|         | LEA      | DX,MES2   |                                                 |

|         | MOV      | АН,09Н    | ; Call for DOS interrupt to                     |

|         | INT      | 21H       | ; display MES2                                  |

|         | JMP      | NEXT      |                                                 |

| LAST :  | LEA      | DX,MES3   | ; Call for DOS interrupt to                     |

|         | MOV      | АН,09Н    | ; display MES3                                  |

|         | INT      | 21H       |                                                 |

|         | VOM      | AH,4CH    | ; Terminate program                             |

9 - 30

Microprocessor

INT

END

END

21H

START

ţ

**Programmable Peripheral Interface 8255**

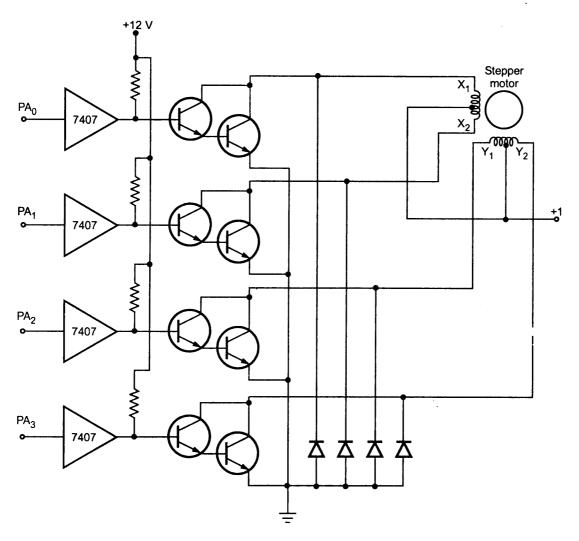

# A stepper motor is a digital motor. It can be driven by digital signal. Fig. 9.25 shows the typical 2 phase motor interfaced using 8255. Motor shown in the circuit has two phases, with center-tap winding. The center taps of these windings are connected to the 12 V supply. Due to this, motor can be excited by grounding four terminals of the two windings. Motor can be retated in store by giving property with the restated in store by giving property.

12 V supply. Due to this, motor can be excited by grounding four terminals of the two windings. Motor can be rotated in steps by giving proper excitation sequence to these windings. The lower nibble of port A of the 8255 is used to generate excitation signals in the proper sequence.

Fig. 9.25 Stepper motor interface

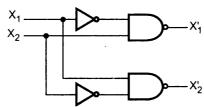

The Table 9.2 shows typical excitation sequence. The given excitation sequence rotates the motor in clockwise direction. To rotate motor in anticlockwise direction we have to excite motor in a reverse sequence. The excitation sequence for stepper motor many change due to change in winding connections. However, it is not desirable to excite both the ends of the same winding simultaneously. This cancels the flux and motor winding may damage. To avoid this, digital locking system must be designed. Fig. 9.26 shows a simple digital locking system. Only one output is activated (made low) when properly excited; otherwise output is disabled (made high).

Fig. 9.26 Digital locking system

| Step | X <sub>1</sub> | X <sub>2</sub> | Y <sub>1</sub> | Y <sub>2</sub> |

|------|----------------|----------------|----------------|----------------|

| 1    | 0              | 1              | 0              | 1              |

| 2    | 1              | 0              | 0              | 1              |

| 3    | 1              | 0              | 1              | 0              |

| 4    | 0              | 1              | 1              | 0              |

| 1    | 0              | 1              | 0              | 1              |

Table 9.2 Full step excitation sequence

The excitation sequence given in Table 9.2 is called **full step sequence**. In which excitation ends of the phase are changed in one step. The excitation sequence given in Table 9.3 takes two steps to change the excitation ends of the phase. Such a sequence is called **half step sequence** and in each step the motor is rotated by 0.9°.

| Step | X <sub>1</sub> | X <sub>2</sub> | Y <sub>1</sub> | Y <sub>2</sub> |

|------|----------------|----------------|----------------|----------------|

| 1    | 0              | 1              | 0              | 1              |

| 2    | 0              | 0              | 0              | 1              |

| 3    | 1              | 0              | 0              | 1              |

| 4    | 1              | 0              | 0              | 0              |

| 5    | 1              | 0              | 1              | 0              |

| 6    | 0              | 0              | 1              | 0              |

| 7    | 0              | 1              | 1              | 0              |

| 8    | 0              | 1              | 0              | 0              |

| 1    | 0              | 1              | 0              | 1              |

Table 9.3 Half step excitation sequence

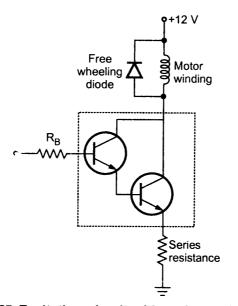

Fig. 9.27 Excitation circuit with series resistance

We know that stepper motor is stepped from one position to the next by changing the currents through the fields in the motor. The winding inductance opposes change in current and this puts limit on the stepping rate. For higher stepping rates and more torque, it is necessary to use a higher voltage source and current limiting resistors as shown in Fig. 9.27. By adding series resistance, we decrease L/R time constant, which allows the current to change more

rapidly in the windings. There is a power loss across series resistor, but designer has to compromise between power and speed.

Example 9.3: Interface stepper motor to the 8086 microprocessor system and write an 8086 assembly language program to control the stepper motor.

**Solution**: Hardware: Fig. 9.28 shows the typical 2 phase motor rated 12V/.67A/ph interfaced with the 8086 microprocessor system using 8255. Motor shown in the circuit has two phases, with center-tap winding. The center taps of these windings are connected to the 12 V supply. Due to this, motor can be excited by grounding four terminals of the two windings. Motor can be rotated in steps by giving proper excitation sequence to these windings. The lower nibble of port A of the 8255 is used to generate excitation signals in the proper sequence. These excitation signals are buffered using driver transistors. The transistors are selected such that they can source rated current for the windings. Motor is rotated by 1.8° per excitation.

Software: As port A is used as an output port, control word for 8255 is 80H.

```

TITLE Stepper Motor Control Program

.MODEL SMALL

.DATA

PORTA EQU 00H ; Port number

CR EQU 06H ; Control Register Address

Excite_code DB 03H,06H,09H,0CH ; code sequence

; for clockwise rotation

```

```

.CODE

; Procedure to rotate a stepper motor clockwise by 90^{\circ}

STEP PROC NEAR

; [ Initialise

MOV AX, @DATA

data segment ]

MOV DS, AX

MOV AL, 80H

; [ Initialise

8255 ]

OUT CR, AL

MOV CL, 32H

; Set repetition count to 50_{10}

RD A1 A2 A2 SET

2778

000000000000

MR-

WR-

A1-

A2-

RESET-

$$$$$

```

Fig 9.28 Stepper motor interface

```

START:

MOV AH, 04H

; Counts excitation sequence

LEA BX, Excite_code

; Initialize pointer

MOV AL, [BX]

; Point to element in Excite_code

BACK1:

OUT PORTA, AL

; Send Excite_code code

CALL DELAY

; Wait

INC BX

; increment pointer

DEC AH

; Repeat 4 times

JNZ BACK1

DEC CL

; Repeat 50 times

JNZ START

RET

STEP

ENDP

```

# 9.14 Control of High Power Devices using 8255

The output port pins of programmable devices can sink current about to 2 mA and source current about few tenth of milliamperes. Thus to interface high power devices such as lights, heaters, solenoids and motors we have to use driver circuit between port pin and the high power device. This section describes various options available to interface high power devices with suitable driver circuits.

# 9.14.1 Integrated Circuit Buffers

One way to increase current sinking and sourcing capacity is to use integrated circuit buffers such as 7406 hex inverting buffer and 7407 hex noninverting buffer. These buffers are of open collector type, therefore their current sourcing capacity is decided by external register. These buffers can sink current as much as 40 mA. This current is sufficient to interface LED displays.

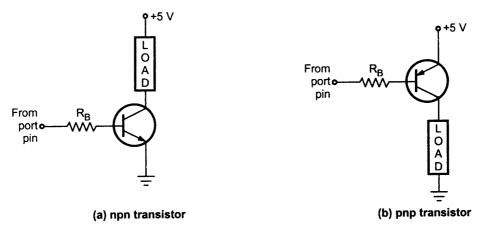

# 9.14.2 Transistor Buffers

The Fig. 9.29 shows some buffer circuits using transistors. In these circuits, transistor is used as a switch. It can be switch ON or OFF with logic 0 or logic 1 on port pin depending on the application. To make transistor ON with logic 0 at port pin we have to use pnp transistor otherwise we have to use npn transistor. When transistor is ON, its collector current drives the load. To determine component values and transistor we have to check maximum collector current of the transistor ( $I_{Cmax}$ ), maximum  $h_{fe}$  that transistor can provide ( $h_{femax}$ ), maximum collector to emitter breakdown voltage ( $V_{BCEO}$ )and a maximum power dissipation (p<sub>dmax</sub>) allowed by the transistor.

9 - 36

Fig. 9.29 Transistor buffer circuits

Let us assume that the load current is 200 mA and maximum sourcing current of port pin is 1 mA. Then transistor should have

$$I_{Cmax} > 200 \text{ mA}$$

$$h_{femin} > \frac{I_C}{I_{Bmax}}$$

$$> \frac{200 \text{ mA}}{1 \text{ mA}}$$

$$\therefore h_{femin} > 200$$

$$P_{dmax} > V_{CEsat} \times I_{Cmax}$$

$$> 0.2 \times 200 \text{ mA}$$

$$> 40 \text{ mW}$$

Assuming output high voltage of port pin equal to 4.5 V we have

$$R_{B} = \frac{4.5 - 0.8}{1 \,\text{mA}}$$

$$= 3.7 \,\text{k}\Omega$$

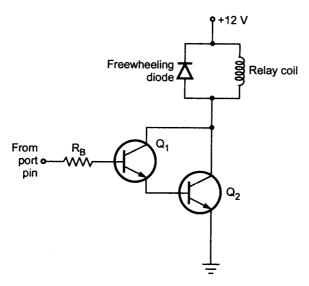

When load current requirements are more, one transistor is not sufficient to provide sufficient current gain. In such situations two transistors in darlington connection are used to provide the necessary current gain. The Fig. 9.30 shows the darling transistor pair used to drive relay or solenoid coil.

Here, the output port pin supplies the base current to transistor  $Q_1$ . This base current produces  $\beta$  times large collector current of  $Q_1$ . The collector current of  $Q_1$  becomes the base current of  $Q_2$  and is amplified by the current gain of  $Q_2$ , i.e.  $\beta_2$ . Therefore, overall current amplification is  $\beta_1 \times \beta_2$ . Usually this amplification is greater than 1000. Many such

Fig. 9.30 Use of darlington transistor to drive relay or solenoid coil

darlington pairs are available. We can use these darlington pair to drive loads upto about 1 A load currents.

As shown in the Fig. 9.30, free wheeling diode is purposely connected when load is inductive such as solenoid, relay and motor. We know that, inductor opposes change in current. When we switch off the transistor, the current in the inductor does not reach to zero immediately; it flows for a while. However, this current cannot flow through transistor, because it is off. Instead, this current develops a voltage across inductor with reverse polarities, i.e. – ve at the top and + ve at in the bottom in given circuit. Usually, this reverse voltage is large enough to break down the transistor. The free wheeling diode provides the path for induced current and clamps the reverse voltage across inductor at 0.7 V.

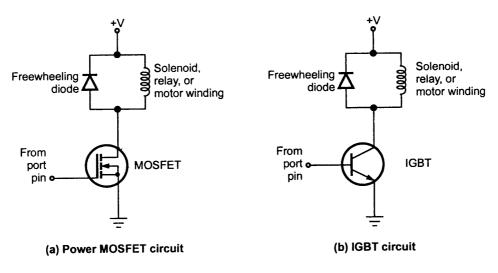

The Fig. 9.31 shows a power driver circuits using MOSFET and IGBT to drive solenoids, relay or motor windings. Power MOSFETS are somewhat more expensive than darlington transistors, but they have the advantage that they require only a voltage to drive them. The IGBT has high input impedance and fast switching speed. They also have low voltage drop and high current carrying capacity.

# 9.14.3 Isolation Circuits

To control 220 V or 440 V ac devices it is not desirable to have a common power circuit ground and control circuit ground. This is very important because if the 220 V ac line gets shorted to the  $V_{CC}$  line of a microcomputer, it usually bakes most of the microcomputer ICs. To avoid this, the control circuit and power circuit is electrically isolated by separating their individual ground lines.

Fig. 9.31 Circuits for driving solenoid, relay or motor winding

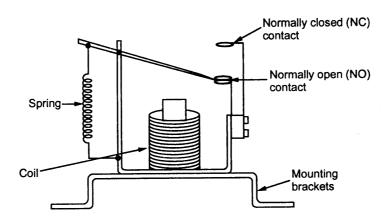

#### 9.14.3.1 Electromagnetic Relays

To control ON/OFF operation of ac devices we can use electromagnetic relay. This relay has both normally open and closed contacts. When a current is passed through the coil of the relay, the switch arm is pulled down, opening the top contact and closing the bottom contact, as shown in the Fig. 9.32.

Fig. 9.32 Electromagnetic relay

The relay contacts are rated for maximum current of about 20A - 25A. These relays are also called mechanical relays because mechanical contact makes the circuit to ON or OFF. The mechanical relays having higher current ratings are sometimes called contactors.